Flip-flop er et begreb, der hører under digital elektronik, og det er en elektronisk komponent, der bruges til at gemme en enkelt bit information.

Diagrammatisk repræsentation af flip flop

- Da flip flop er et sekventielt kredsløb, er dets input baseret på to parametre, den ene er den aktuelle input, og den anden er outputtet fra den tidligere tilstand.

- Den har to udgange, begge komplementerer hinanden.

- Det kan være i en af to stabile tilstande, enten 0 eller 1.

Grundlæggende diagram af flip flop

Hvad er T Flip Flop?

- T-flip flop eller for at være præcis er kendt som Toggle Flip Flop, fordi det kan skifte output afhængigt af input.

- T her står for Skift .

- Toggle angiver grundlæggende, at bit'en vil blive vendt, dvs. enten fra 1 til 0 eller fra 0 til 1.

- Her tilføres en clock-impuls til at betjene dette flop, derfor er det en clocket flip-flop.

Konstruktion af T Flip Flop

Vi kan konstruere T flip på tre måder, nemlig:

- Ved at bruge SR Flip Flops.

- Ved at bruge D Flip Flops.

- Ved at bruge JK Flip Flops

Måder at konstruere T Flip Flop

Lad os se konstruktionen af T Flip Flop ved hjælp af SR Flip Flops, som kræver 2 AND-porte og 2 NOR-porte som vist nedenfor:

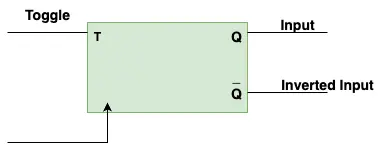

Grundlæggende blokdiagram af T Flip Flop

Her indeholder blokdiagram Toggle og clock input, Q og Q' er de supplerede inputs.

Bearbejdning af T Flip Flop

Tilfælde 1 : Lad os sige, T = 0 og urets puls er høj dvs. 1, så vil output fra begge, OG gate 1, AND gate 2 være 0 , port 3 output vil være Q og tilsvarende port 4 output vil være Q' så både værdierne af Q og Q' er de samme som deres tidligere værdi, hvilket betyder Hold tilstand .

Tilfælde 2 : Lad os sige, T=1 , så vil udgangen af både OG gate 1 være (T * ur * Q) , og da T og clock begge er 1, så vil udgangen af AND gate 1 være Q , og på samme måde vil output fra AND-port 2 være (T * ur * Q') dvs. Q' . Nu vil gate 3-udgang være (Q'+Q)' og lad os sige, at Q' er nul, så vil gate 3-udgang være (0+Q)' hvilket betyder Q' og tilsvarende gate 4 output vil være (Q+Q')' og da Q' er nul, så gate 4 output vil være Q', hvilket betyder 0 da Q' er nul. Derfor kan vi i dette tilfælde sige, at udgangen skifter, fordi T=1 .

Truth Table of T Flip Flop

- Her er T Toggle-input, Q er nuværende tilstandsinput, Qt+1 er næste tilstandsoutput.

- Herfra kan vi se, at når Toggle (T) er 0, er næste tilstandsoutput (Qt+1) det samme som nuværende tilstandsinput (Q).

- Hver gang Toggle (T) er 1, vil næste tilstandsoutput (Qt+1) være et komplement til den nuværende tilstandsinput (Q), hvilket betyder, at den skiftes.

Karakteristisk ligning

- Den karakteristiske ligning fortæller os om, hvad der vil være den næste tilstand af flip flop i forhold til nuværende tilstand.

- For at få den karakteristiske ligning konstrueres K-Map, som vil blive vist som nedenfor:

- Hvis vi løser ovenstående K-Map, vil den karakteristiske ligning være Q(n+1) = TQn’ + T’Qn = T XOR Qn

Excitationstabel

Excitationstabel fortæller grundlæggende om den excitation, som kræves af flip flop for at gå fra nuværende tilstand til næste tilstand.

- Her, når T er 0, er Qt+1 det samme som input Q.

- Og når T er 1, er Qt+1 kompliment af input Q.

Anvendelser af T Flip Flop

Der er adskillige anvendelser af T Flip Flop i Digital System, som er anført nedenfor:

- Tællere : T Flip Flops brugt i skranker. Tællere tæller antallet af hændelser, der opstår i et digitalt system.

- Data opbevaring : T Flip Flops bruges til at skabe hukommelse, som bruges til at gemme data, når strømmen er slukket.

- Synkrone logiske kredsløb : T flip-flops kan bruges til at implementere synkrone logiske kredsløb, som er kredsløb, der udfører operationer på binære data baseret på et kloksignal. Ved at synkronisere det logiske kredsløbs operationer med clocksignalet ved hjælp af T-flip-flops, kan kredsløbets adfærd gøres forudsigelig og pålidelig.

- Frekvensopdeling : Den bruges til at dividere frekvensen af et clock-signal med 2. Flip-flop vil skifte dets output hver gang clock-signalet går fra høj til lav eller lav til høj, og dermed dividere clock-frekvensen med 2.

- Skifteregistre : T flip-flops kan bruges i skifteregistre, som bruges til at skifte binære data i én retning.

Konklusion

I denne artikel tager vi udgangspunkt i det grundlæggende i flip flops, at hvad der faktisk er flip flops, og derefter diskuterede vi om T flip flops, tre to måder, hvorpå vi kan konstruere T flip flops, det er grundlæggende blokdiagram, arbejde af T flip flop , det er Sandhedstabel, Karakteristisk ligning samt Excitationstabel, og til sidst diskuterede vi anvendelserne af T Flip Flops.